Servizi di produzione elettronica completi, ti aiutano a realizzare facilmente i tuoi prodotti elettronici da PCB e PCBA

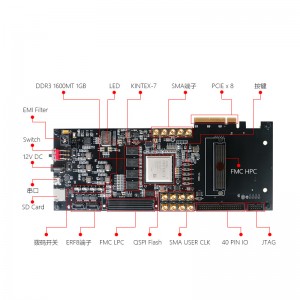

FPGA Xilinx K7 Kintex7 PCIe comunicazione in fibra ottica

- DDR3 SDRAM: 16 GB DDR3 bus a 64 bit, velocità dati 1600 Mbps

- QSPI Flash: un pezzo di QSPIFLASH da 128 Mbit, che può essere utilizzato per i file di configurazione FPGA e l'archiviazione dei dati utente

- Interfaccia PCLEX8: l'interfaccia PCLEX8 standard viene utilizzata per comunicare con la scheda madre del computer tramite la porta PCIE. Supporta lo standard PCI Express 2.0. La velocità di comunicazione a canale singolo può raggiungere i 5 Gbps.

- Porta seriale USB UART: una porta seriale, da collegare al PC tramite il cavo miniUSB per eseguire la comunicazione seriale

- Scheda Micro SD: la scheda MicroSD è posizionata in modo tale che sia possibile collegare la scheda MicroSD standard

- Sensore di temperatura: un chip sensore di temperatura LM75, in grado di monitorare la temperatura ambientale attorno alla scheda di sviluppo

- Porta di estensione FMC: un FMC HPC e un FMCLPC, che possono essere compatibili con varie schede di espansione standard

- Terminale di connessione ad alta velocità ERF8: 2 porte ERF8, che supportano la trasmissione del segnale ad altissima velocità Estensione a 40 pin: riservata un'estensione generale Interfaccia IO con 2,54 mm 40 pin, O effettivo ha 17 coppie, supporta 3,3 V

- La connessione periferica del livello e del livello 5V può collegare le periferiche periferiche di diverse interfacce 1O per uso generale

- Terminale SMA; 13 testine SMA placcate in oro di alta qualità, che consentono agli utenti di collaborare con schede di espansione FMC AD/DA ad alta velocità per la raccolta e l'elaborazione del segnale

- Gestione del clock: sorgente multi-clock. Tra queste, la sorgente di clock differenziale di sistema a 200 MHz SIT9102

- Oscillazione differenziale al cristallo: cristallo da 50 MHz e chip di gestione dell'orologio programmabile SI5338P: dotato anche di

- 66 MHz EMCCLK. Può adattarsi con precisione a diverse frequenze di clock di utilizzo

- Porta JTAG: porta JTAG standard da 10 punti da 2,54 mm, per il download e il debug dei programmi FPGA

- Chip di monitoraggio della tensione di sub-reset: un pezzo di chip di monitoraggio della tensione ADM706R e il pulsante con il pulsante fornisce un segnale di reset globale per il sistema

- LED: 11 luci LED, indicano l'alimentazione della scheda, il segnale config_done, FMC

- Segnale indicatore di alimentazione e 4 LED utente

- Chiave e interruttore: 6 chiavi e 4 interruttori sono pulsanti di reset FPGA,

- Il pulsante Programma B e 4 tasti utente sono composti. 4 interruttori a doppio comando a lama singola

Scrivi qui il tuo messaggio e inviacelo

Categorie di prodotti

-

Telefono

-

E-mail

-

WhatsApp

-

Skype

-

Skype

-

Skype